# SPI/SPIDEV for IoT

Tom King

tk@amfmssb.com

cc by sa 3.0

Brought to you by:

- Linux Foundation Training has provided speaker funding

- ARM is subsidizing the manufacturing of the floral bonnet for LCA2019

# What is SPI?

- Serial Peripheral Interface

- Motorola

- de facto standard

- master-slave bus

- 4 wire bus

- except when it's not

- no maximum clock speed

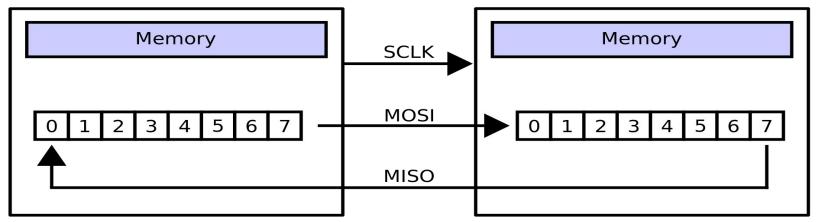

- "A glorified shift register"

http://wikipedia.org/wiki/Serial\_Peripheral\_Interface

#### Common uses of SPI

- Flash memory

- ADCs

- Chromium Embedded Controller

- LCD Controllers

- Sensors

- Thermocouples and other high data rate devices

Advantages:

- Full Duplex in default mode

- Uses 4 pins (or 3 in some implementations)

- Low Processor overhead (even bit banged)

- No "unique address" needed (often just setting a GPIO pin to address)

- No "Protocol" to decode. (although can be used as transport for Protocols)

Disadvantages:

- Higher pin count than i2c

- No in-band addressing (need HW pins to address)

- No slave ack tha the data/command got to the intended recipient.

- No error checking

- Relatively short distances (often only onboard)

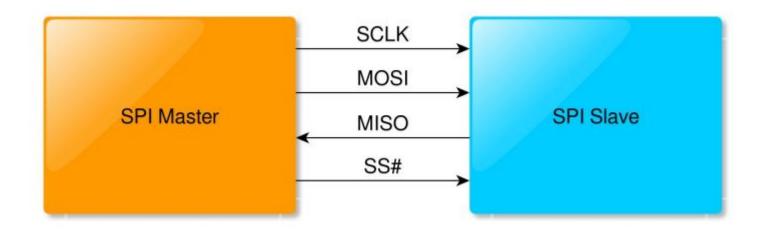

SPI Signals

- MOSI Master Output Slave Input

- SIMO, SDI, DI, SDA

- MISO Master Input Slave Output

SOMI, SDO, DO, SDA

- SCLK Serial Clock (Master output)

SCK, CLK, SCL

- $\overline{SS}$  Slave Select (Master output)

- CSn, EN, ENB

#### **SPI** Master and Slave

#### Slave

By I, Cburnett, CC BY-SA 3.0,

https://commons.wikimedia.org/w/index.php?curid=2302801

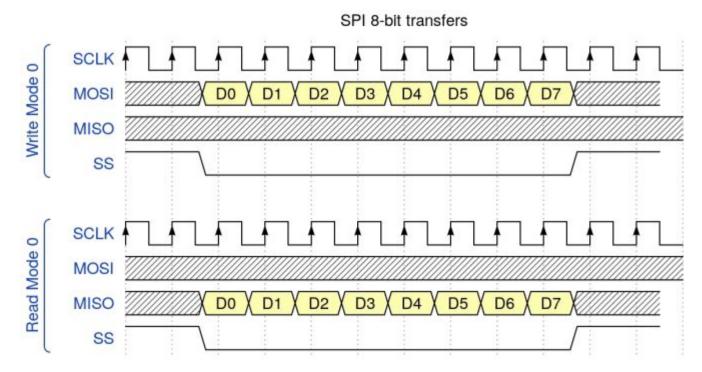

#### **Basic SPI Timing Diagram**

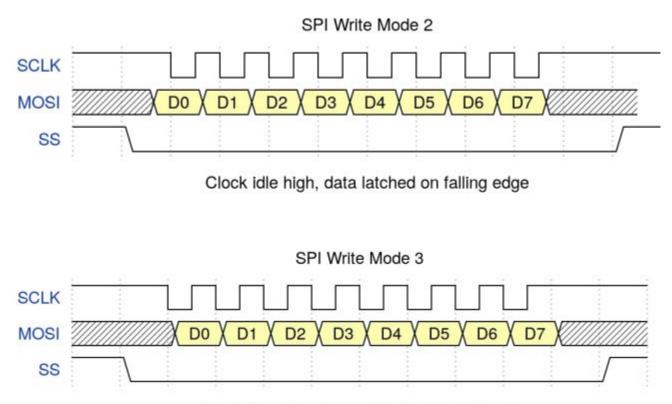

#### SPI Modes

- Modes are composed of two clock characteristics

- CPOL clock polarity

- $\circ$  0 = clock idle state low

- 1 = clock idle state high

- CPHA clock phase

- 0 = data latched falling, output rising

- 1 = data latched rising, output falling

SPI Modes Cont'd

| Mode | CPOL | СРНА |

|------|------|------|

| 0    | 0    | 0    |

| 1    | 0    | 1    |

| 2    | 1    | 0    |

| 3    | 1    | 1    |

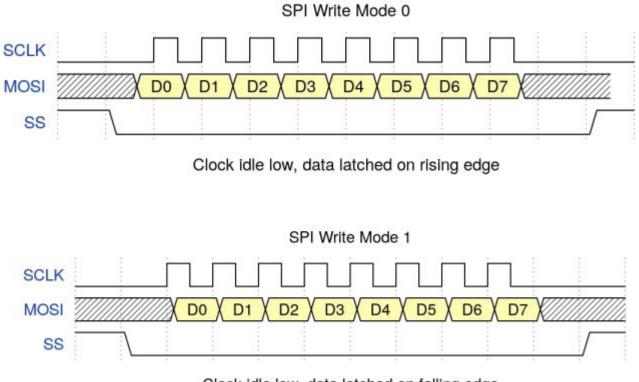

#### SPI Mode Timing - CPOL 0

Clock idle low, data latched on falling edge

#### SPI Mode Timing - CPOL 1

Clock idle high, data latched on rising edge

Let's look at an example together:

https://en.wikipedia.org/wiki/Serial\_Peripheral\_Interface#Example\_of\_bit-banging\_ the\_master\_protocol

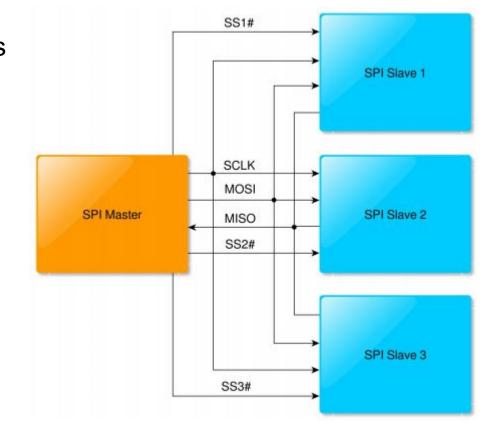

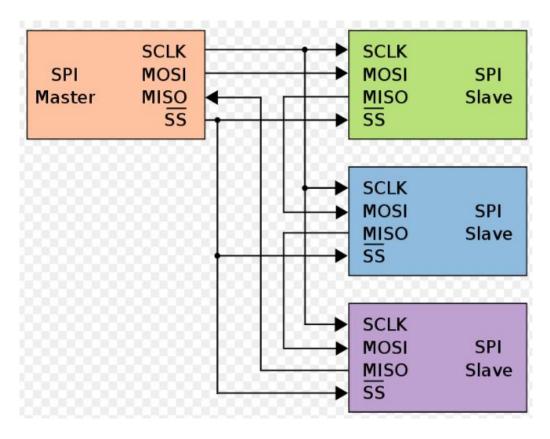

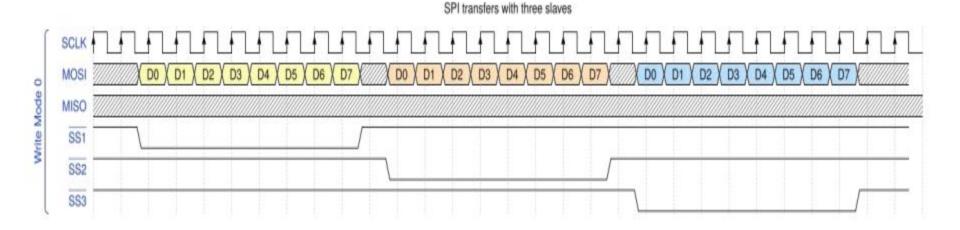

### SPI can be more complicated

- Multiple SPI Slaves

- One chip select for each slave

- Daisy Chaining

- Inputs to Outputs

- Chip Selects

- Dual or Quad SPI (or more lanes)

- Implemented in high speed SPI Flash devices

- Instead of one MISO, have N MISOs

- N times bandwidth of traditional SPI

- 3 Wire (Microwire) SPI

- Combined MISO/MOSI signal operates in half duplex

**Multiple SPI Slaves**

## SPI Daisy Chain

By en:User:Cburnett - Own workThis W3C-unspecified vector image was created with Inkscape., CC BY-SA 3.0, https://commons.wikimedia.org/w/index.php?curid=1482275

#### SPI Mode Timing - Multiple Slaves

Conclusions:

- Old Reliable Bus

- Still quite popular

- New variants are making it even more useful (QSPI, etc)